Da man immer mal wieder darauf trifft, habe ich mich entschieden, einen kurzen Beitrag darüber zu schreiben.

Es geht um das Negationssymbol, ein Kreis (engl meist bubble genannt) am Eingang von Logikgattern.

Hinweis: zum Vergrössern der Abbildung auf das Bild klicken!

Zurück gehen diese Symbole anscheinend auf eine Norm beim amerikanischen (und später auch beim japanischen) Militär,

weswegen diese Symbole mitunter auch als MIL-Symbole bezeichnet werden, zumindest hier in Japan.

Im Zusammenhang damit fallen oft die Begriffe positive und negative Logik.

Einfachstes Beispiel für rein positive Logik ist der digitale Puffer (engl. buffer): was reinkommt, kommt auch unverändert wieder raus: Y = A.

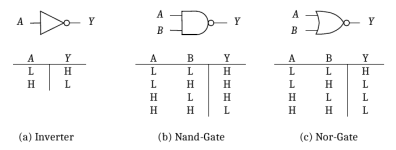

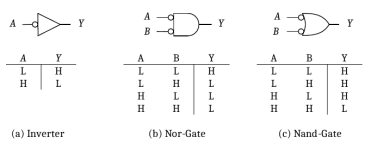

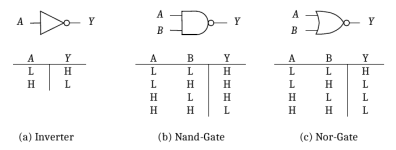

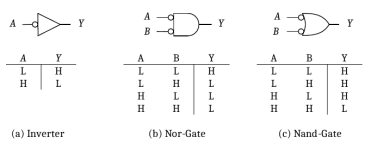

Ist der Eingang LOW, ist auch der Ausgang LOW. Anders beim Inverter, NOT-Gate: ist der Eingang LOW, dann ist der Ausgang HIGH.

Diese Inversion (Umkehrung bzw. Negation) kennzeichnet man durch das Kreissymbol am Ausgang des Inverters.

Hier liegt eine gemischte Logik vor, positiv am Eingang, negativ am Ausgang.

Es gibt ausserdem die Konvention, dass man nur Eingänge und Ausgänge gleicher Logik miteinander verbindet.

Das soll helfen, den Betriebszustand der Schaltung intuitiv zu erfassen. Beispiel:

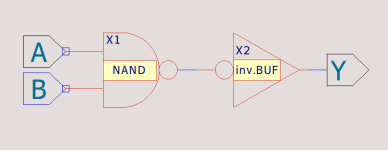

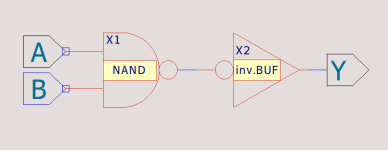

Der Ausgang des NANDs wie auch der Eingang des invertierenden Puffers sind negative Logik.

Sind A und B LOW, so ist auch der Ausgang Y LOW, sind A und B HIGH, ist auch Y HIGH.

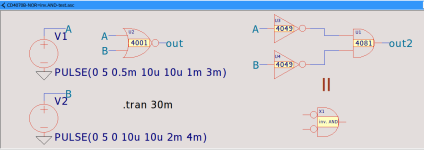

Man muss aber beim Zusammenschalten auch die Wahrheitstabellen im Auge behalten. So ist etwa ein AND-Gatter,

dessen Eingänge negiert sind, nicht – wie man vielleicht meinen könnte – ein NAND, sondern es entspricht einem NOR-Gatter,

wie man beim aufmerksamen Betrachten der nachfolgenden Grafiken leicht erkennen wird.

Das einzige Gatter, bei dem sich kein Unterschied einstellt, ist der Inverter. Das AND-Gatter mit invertierten Eingängen ergibt ein NOR,

und das OR-Gatter mit invertierten Eingängen resultiert in einem NAND-Gatter.

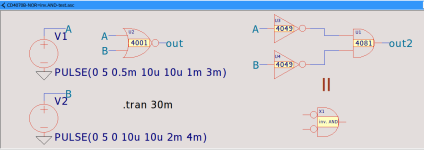

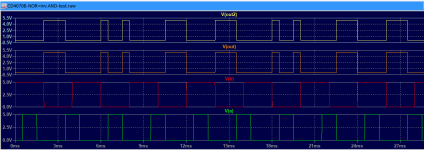

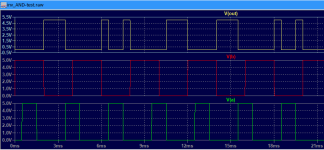

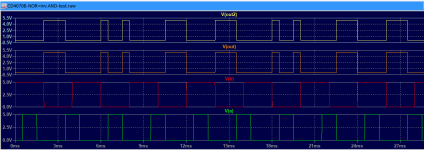

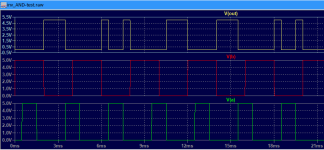

Diese Zusammenhänge lassen sich auch experimentell in der Simulation bestätigen, siehe dazu die nachfolgenden Screenshots.

Alle notwendigen Dateien befinden sich wie immer im Archiv.

RudiS

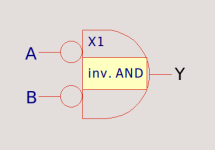

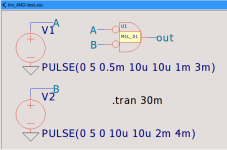

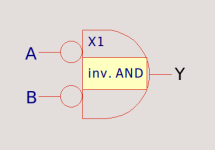

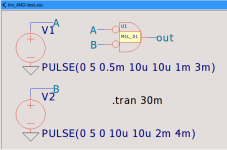

P.S.: Ich habe mal zum Experimentieren ein invert-AND (Symbol und Subcircuit) zusätzlich angehängt. Man kann z.B. in der beigefügten .asc-Datei das NOR durch dieses inv_AND ersetzen.

Wenn ich Zeit habe, werde ich alle anderen MIL-Gatter basteln.

Es geht um das Negationssymbol, ein Kreis (engl meist bubble genannt) am Eingang von Logikgattern.

Hinweis: zum Vergrössern der Abbildung auf das Bild klicken!

Zurück gehen diese Symbole anscheinend auf eine Norm beim amerikanischen (und später auch beim japanischen) Militär,

weswegen diese Symbole mitunter auch als MIL-Symbole bezeichnet werden, zumindest hier in Japan.

Im Zusammenhang damit fallen oft die Begriffe positive und negative Logik.

Einfachstes Beispiel für rein positive Logik ist der digitale Puffer (engl. buffer): was reinkommt, kommt auch unverändert wieder raus: Y = A.

Ist der Eingang LOW, ist auch der Ausgang LOW. Anders beim Inverter, NOT-Gate: ist der Eingang LOW, dann ist der Ausgang HIGH.

Diese Inversion (Umkehrung bzw. Negation) kennzeichnet man durch das Kreissymbol am Ausgang des Inverters.

Hier liegt eine gemischte Logik vor, positiv am Eingang, negativ am Ausgang.

Es gibt ausserdem die Konvention, dass man nur Eingänge und Ausgänge gleicher Logik miteinander verbindet.

Das soll helfen, den Betriebszustand der Schaltung intuitiv zu erfassen. Beispiel:

Der Ausgang des NANDs wie auch der Eingang des invertierenden Puffers sind negative Logik.

Sind A und B LOW, so ist auch der Ausgang Y LOW, sind A und B HIGH, ist auch Y HIGH.

Man muss aber beim Zusammenschalten auch die Wahrheitstabellen im Auge behalten. So ist etwa ein AND-Gatter,

dessen Eingänge negiert sind, nicht – wie man vielleicht meinen könnte – ein NAND, sondern es entspricht einem NOR-Gatter,

wie man beim aufmerksamen Betrachten der nachfolgenden Grafiken leicht erkennen wird.

Das einzige Gatter, bei dem sich kein Unterschied einstellt, ist der Inverter. Das AND-Gatter mit invertierten Eingängen ergibt ein NOR,

und das OR-Gatter mit invertierten Eingängen resultiert in einem NAND-Gatter.

Diese Zusammenhänge lassen sich auch experimentell in der Simulation bestätigen, siehe dazu die nachfolgenden Screenshots.

Alle notwendigen Dateien befinden sich wie immer im Archiv.

RudiS

P.S.: Ich habe mal zum Experimentieren ein invert-AND (Symbol und Subcircuit) zusätzlich angehängt. Man kann z.B. in der beigefügten .asc-Datei das NOR durch dieses inv_AND ersetzen.

Wenn ich Zeit habe, werde ich alle anderen MIL-Gatter basteln.

Anhänge

Zuletzt bearbeitet: